공신력 있는 교육 운영

고용노동부 성과평가 최우수 'S등급' 달성 기관. 명지대학교의 반도체 설계 인력 양성 노하우와 검증된 인프라를 통해 차별화된 교육 환경을 제공합니다.

모집기간: 2026.05.08까지

기간

960시간 / 6개월 몰입 과정

교육기간: 2026.06.15~2026.12.07 교육시간: 월~금 9:00~5:50

방식

반도체 설계 툴 중심 집중 교육

실습 및 프로젝트 비중 50% 이상

커리큘럼 특징

글로벌 표준 Synopsys EDA 툴 기반 실습 환경

결과

현업에 즉시 투입 가능한 반도체 설계 전문가 양성

PROGRAM OVERVIEW

RTL 모델링부터 GDSII Sign-off까지, 반도체 전 공정 Full-Stack 설계를 관통하는 실전 커리큘럼. 명지대학교 KDT 과정은 HDL(하드웨어 설계 언어)부터 Sign-off(최종 설계 검증)까지 반도체 설계의 전 과정을 단계적으로 교육합니다. 특히 세계 시장 점유율 1위인 Synopsys사의 글로벌 표준 EDA 툴을 활용하여, 기업 현장에서 즉시 투입 가능한 수준의 R&D 설계 역량을 완성합니다.

Full-Stack 설계 프로세스 습득 (RTL 설계부터 Layout까지 전 과정 교육)

실무 기반 고난도 프로젝트 수행 (32nm 기반 CISC 구조 CPU 및 시스템 통합 설계)

현업 수준의 설계 포트폴리오 (HDL to GDSII 결과물을 통한 취업 경쟁력 확보)

BRAND POSITIONING

이론이 아닌, 실제 설계를 경험하는 과정입니다. 프로젝트 기반 실습을 통해 직접 설계를 수행하고 현업에서 활용 가능한 수준의 결과물을 완성합니다.

고용노동부 성과평가 최우수 'S등급' 달성 기관. 명지대학교의 반도체 설계 인력 양성 노하우와 검증된 인프라를 통해 차별화된 교육 환경을 제공합니다.

전체 교육의 50%를 차지하는 480시간의 설계 프로젝트. 'Plan-Do-Check-Act' 4단계 관리 체계를 통해 AI 프로세서 및 CISC CPU 등 고난도 IP 설계 결과물을 직접 완성합니다.

Synopsys 글로벌 표준 설계 툴(EDA-Tool) 기반 실무 훈련. RTL 설계부터 Physical Implementation까지, HDL to Sign-off 전 과정을 아우르는 실전형 커리큘럼을 제공합니다.

팹리스와 디자인하우스 등 산업계 수요를 반영한 현장 밀착형 교육으로 수료 후 즉시 투입 가능한 R&D 설계 전문가를 배양합니다

APPLICATION FLOW

설계 역량과 취업 의지를 확인하는 체계적인 선발 프로세스. 참여기업 인사 책임자가 직접 면접에 참여하여 실무에 적합한 인재를 선발합니다.

모집 기간

2026년 4월 27일 ~ 5월 8일

※ 모집 인원 충원 시 조기 마감될 수 있습니다

선발 절차

5월 중순 ~ 6월 초

서류 심사 및 기업 연계 면접

최종 합격

2026년 6월 중

개별 안내 및 등록 절차 진행

교육 시작

2026년 6월 15일(월) 개강

명지대학교 용인캠퍼스 제2공학관 5층(Y8501호)

선발 기준

관련 학과 4학년 및 졸업생 (전기, 전자, 반도체, 정보통신, 컴퓨터공학 등) 또는 프로그래밍(C/C++, Python) 가능자 우대

CLASSROOM

명지대학교 용인캠퍼스 제2공학관 내 전용 실습실에서 1인 1 PC 환경으로 실습이 진행됩니다. 전 세계 시장 점유율 1위인 Synopsys사의 EDA 툴 라이선스를 활용하여 실제 칩 제작 공정(HDL to GDSII) 전 과정을 완벽히 재현합니다.

오전 8시부터 오후 10시까지 개방되는 훈련생 전용 몰입형 설계 공간

장비 및 소프트웨어

실습 장비 및 소프트웨어 확보에만 약 1억 원 이상의 예산 투입

전담 지원

실습 효율 극대화를 위한 전문 보조강사 2인 상시 배치

안전 보장

CCTV 설치 및 전용 보안 시스템을 통한 안전한 학습 환경

※ 명지대학교는 Synopsys 교육용 공식 교재를 개인별로 제공합니다.

CURRICULUM

석사급 2년 교육 과정에 준하는 총 960시간의 압도적인 훈련량을 자랑합니다. 반도체 설계의 기초인 HDL부터 최종 검증 단계인 Sign-off까지, 글로벌 표준 Synopsys EDA 툴을 활용하여 실무와 동일한 프로세스를 경험합니다. 전체 과정의 50% 이상을 차지하는 **실전 프로젝트(480시간)**를 통해 기업이 즉시 원하는 수준의 설계 포트폴리오를 완성하십시오.

01

Synopsys Front-End 솔루션을 활용한 고정밀 RTL 설계 및 32nm 공정 기반의 논리 합성 실무 역량 내재화: 현업에서 가장 널리 쓰이는 Verilog HDL을 활용하여 복잡한 디지털 로직을 설계하고, Synopsys Design Compiler를 통해 최적화된 게이트 레벨 네트리스트를 생성하는 전 과정을 심도 있게 학습합니다.

02

Synopsys EDA 툴 기반의 디지털 반도체 BE 설계 및 레이아웃 최적화를 통한 Physical Design 전 공정 마스터: Floorplan부터 Place & Route, Clock Tree Synthesis(CTS)를 거쳐 타이밍 클로저(Timing Closure)를 달성하는 하이엔드 설계 기법을 습득하고, 실제 칩 제작이 가능한 수준의 물리적 설계를 완수합니다.

03

Synopsys TCAD를 활용한 차세대 CMOS 소자 최적화 및 뉴로모픽 메모리 아키텍처 시뮬레이션 및 분석: 반도체 소자의 물리적 특성을 이해하고, TCAD 툴을 이용해 나노미터급 소자 공정을 시뮬레이션합니다. 특히 차세대 지능형 반도체의 핵심인 뉴로모픽 메모리 소자의 설계 인프라를 학습하여 미래 기술 대응력을 높입니다.

04

Cadence Virtuoso 및 Spice를 이용한 고성능 아날로그/혼성신호 IC 설계 및 레이아웃 실무 최적화: 업계 표준인 Cadence 툴을 활용하여 증폭기(Amplifier) 등 필수 아날로그 회로를 설계합니다. 회로의 물리적 배치인 레이아웃 실습을 통해 기생 성분을 최소화하고 칩 성능을 극대화하는 노하우를 습득합니다.

05

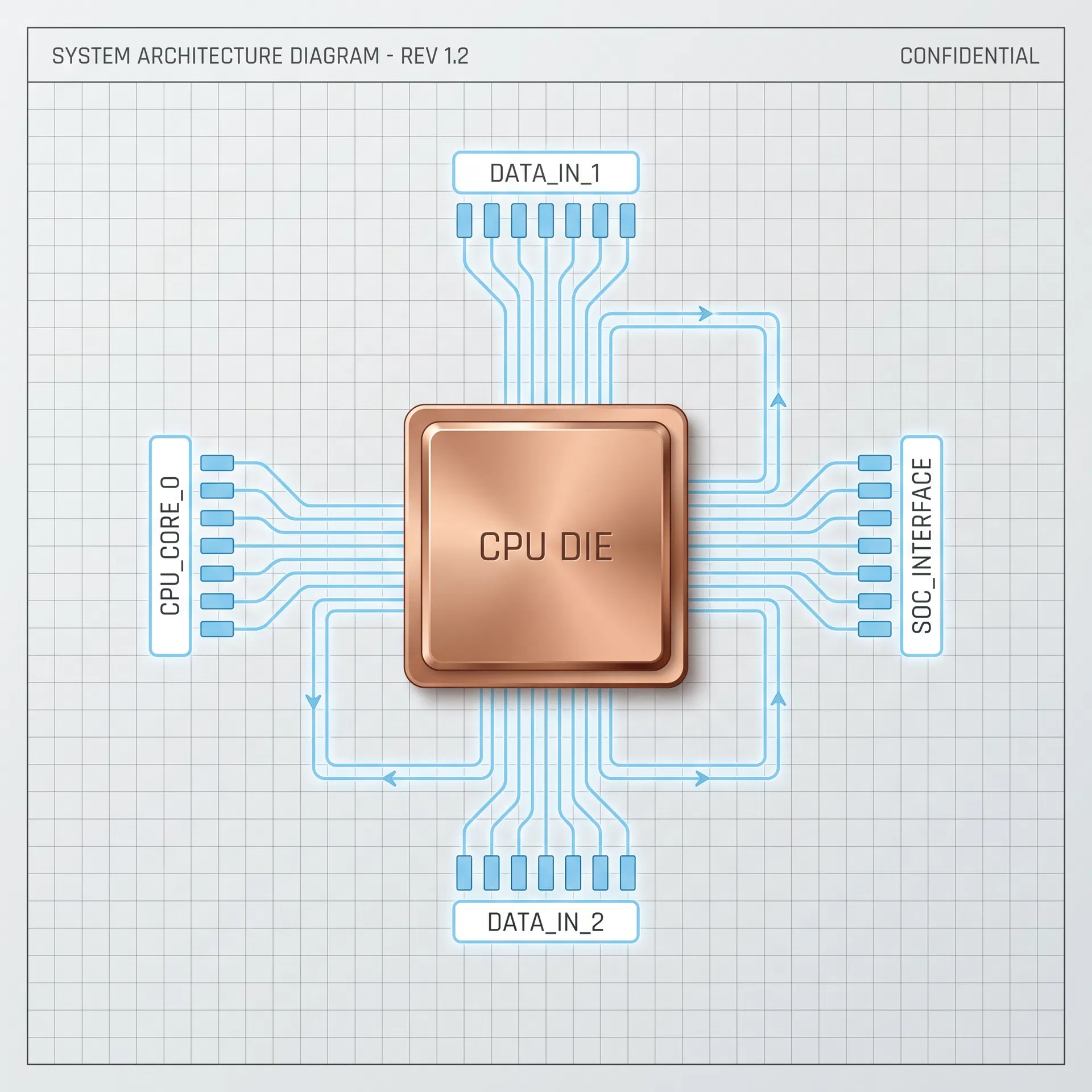

Xilinx Vivado 기반의 RTL 설계 응용 및 SoC 아키텍처 최적화 역량 확보: FPGA 환경에서 실제 SoC 시스템이 구동되는 메커니즘을 심도 있게 이해하고, 아키텍처 설계의 기초부터 시스템 통합 및 검증까지의 과정을 실습합니다. 하드웨어와 소프트웨어의 유기적인 결합을 통해 최적화된 시스템 온 칩(SoC)을 설계하고, 실제 보드 상에서 동작을 검증하는 실무 기술을 마스터합니다.

06

32nm 미세 공정 라이브러리를 활용한 ORCA(Open RISC Architecture) 기반 프로세서 Full-Flow 설계: 오픈 소스 RISC 아키텍처인 ORCA를 바탕으로 실제 칩 제작이 가능한 수준의 프로세서를 설계합니다. RTL 설계부터 Synopsys 툴을 이용한 논리 합성, 물리적 설계(Physical Design) 및 최종 Sign-off까지 반도체 설계의 전 과정을 수행하며, 32nm 공정 환경에서의 타이밍 클로저와 전력 최적화 실무를 완벽히 체득합니다.

07

CISC 아키텍처 기반 CPU Core 설계와 주변 장치(Peripherals) 간의 시스템 통합 및 최적화: 복잡한 명령어 세트를 처리하는 CISC 프로세서를 설계하고, 메모리 및 I/O 인터페이스와의 유기적인 시스템 통합을 실습합니다. 하드웨어 설계의 꽃이라 불리는 CPU 전체 동작 사이클을 구현함으로써, 저수준(Low-level) 제어부터 고수준 시스템 설계까지 아우르는 최상위 엔지니어 역량을 확보합니다.

08

반도체 공정 및 품질 관리 실무 검증과 프로젝트 결과물 발표를 통한 전문가 피드백 및 평가: 실제 제작 가능한 수준으로 완성된 프로젝트 포트폴리오를 발표하고 전문가의 평가를 받습니다. 반도체 양산 공정과 품질 관리의 핵심 이슈를 정리하며 실무형 인재로서의 최종 검증을 마칩니다.

BENEFITS

교육비 지원부터 훈련장려금, 실습 환경까지 학습에 집중할 수 있는 조건을 제공합니다.

본 과정은 국가가 교육비의 대부분을 지원하는 K-디지털 트레이닝 사업으로 운영됩니다. 총 교육비 약 1,745만 원 중 개인부담금 50만 원을 제외한 전액을 국가가 지원하여 수강생의 경제적 부담을 획기적으로 낮췄습니다. 수준 높은 설계 인프라와 교육 커리큘럼을 직접 확인하십시오.

매월 30만원 이상의 훈련장려금을 지급하며, 국민취업지원제도 참여 시 (해당자에 한함) 추가 수당을 지원받을 수 있습니다.

훈련 과정을 성공적으로 수료한 명지대학교 전자공학전공 재학생에게는 12학점까지 학점 인정 혜택을 부여하여 학업과 취업 준비를 병행할 수 있도록 돕습니다.

글로벌 표준 Synopsys와 Cadence EDA 툴은 물론, Xilinx SoC 보드까지 1인 1환경으로 제공되어 기다림 없는 실습이 가능합니다. 최적의 설계 인프라가 갖춰진 전용 공간에서 석사급 프로젝트의 전 과정을 온전히 경험하십시오.

ELIGIBILITY

아래 조건을 충족하는 경우 지원 가능합니다. 간단한 확인으로 지원 가능 여부를 판단하세요.

반도체, 전기, 전자, 정보통신, 컴퓨터 및 관련 학과 3년 이상 수료자 비 전공자도 기초 역량 확보 시 지원 가능합니다.

내일배움카드 발급 가능 미취업자 및 졸업 예정자 4학년 졸업 예정자 및 일반 미취업자를 중심으로 선발합니다. 적극적인 취업 의지 보유자를 환영합니다.

프로그래밍 및 설계 기초 역량 보유자 우대 C/C++, 파이썬 등 1개 이상의 프로그래밍 가능자. Verilog-HDL 하드웨어 설계 언어 경험자 및 반도체 관련 자격증 소지자는 가점이 부여됩니다.

지원 전 마지막 체크

주 5일, 1일 8시간 (월~금 09:00~17:50) 오프라인 대면 훈련 참여 가능자

FAQ

버튼을 눌러 답변을 확인하세요

CONTACT

정원 모집시 조기 마감될 수 있습니다. 아래 버튼을 통해 바로 신청 또는 문의가 가능합니다. 상세한 상담이 필요하시면 명지대학교 KDT 사업단 ([email protected] / 031-324-1295)로 문의해 주시기 바랍니다.

모집기간: 2026.05.08까지